12:10 LAN тестер (вторая редакция). | ||||||||

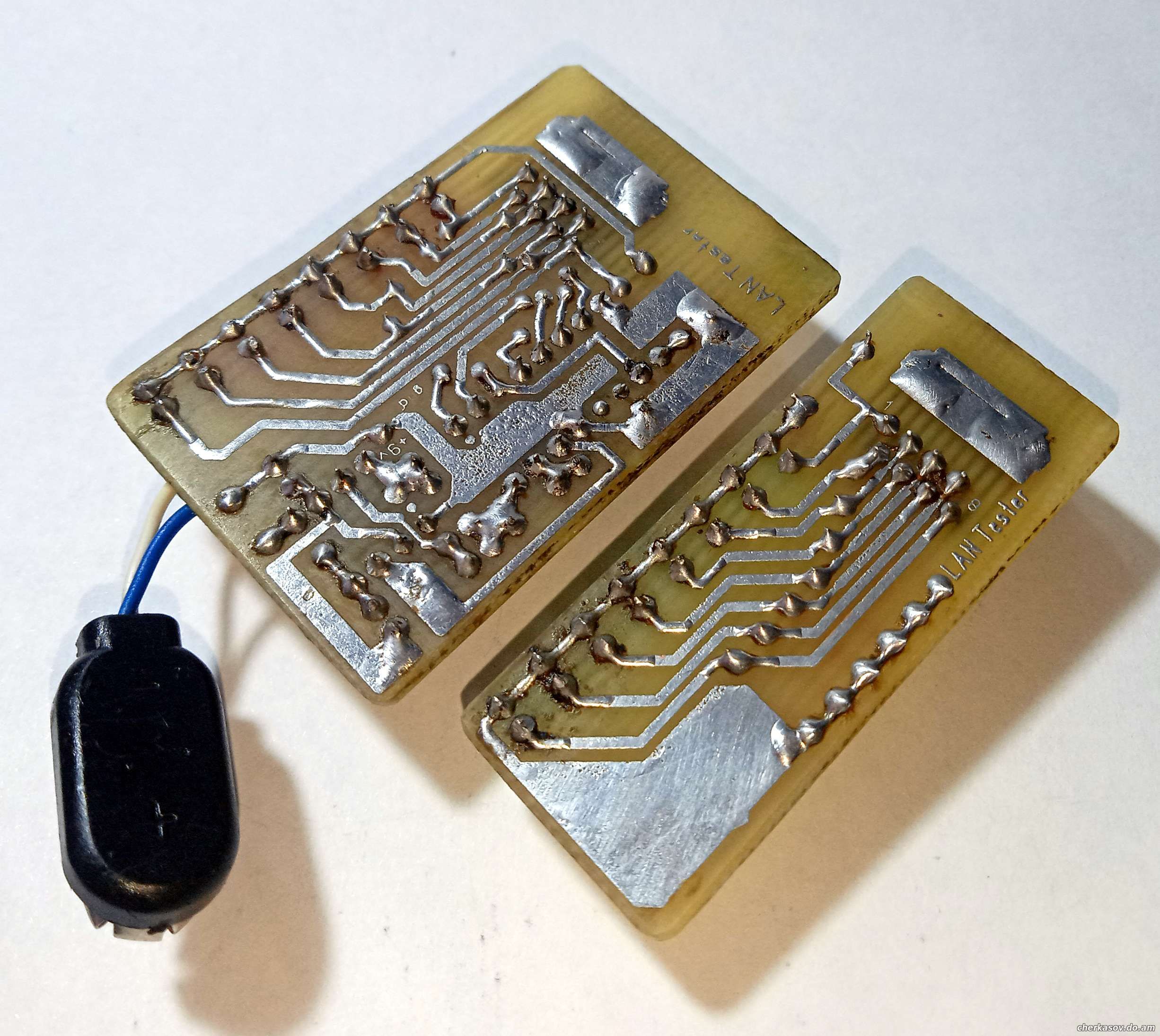

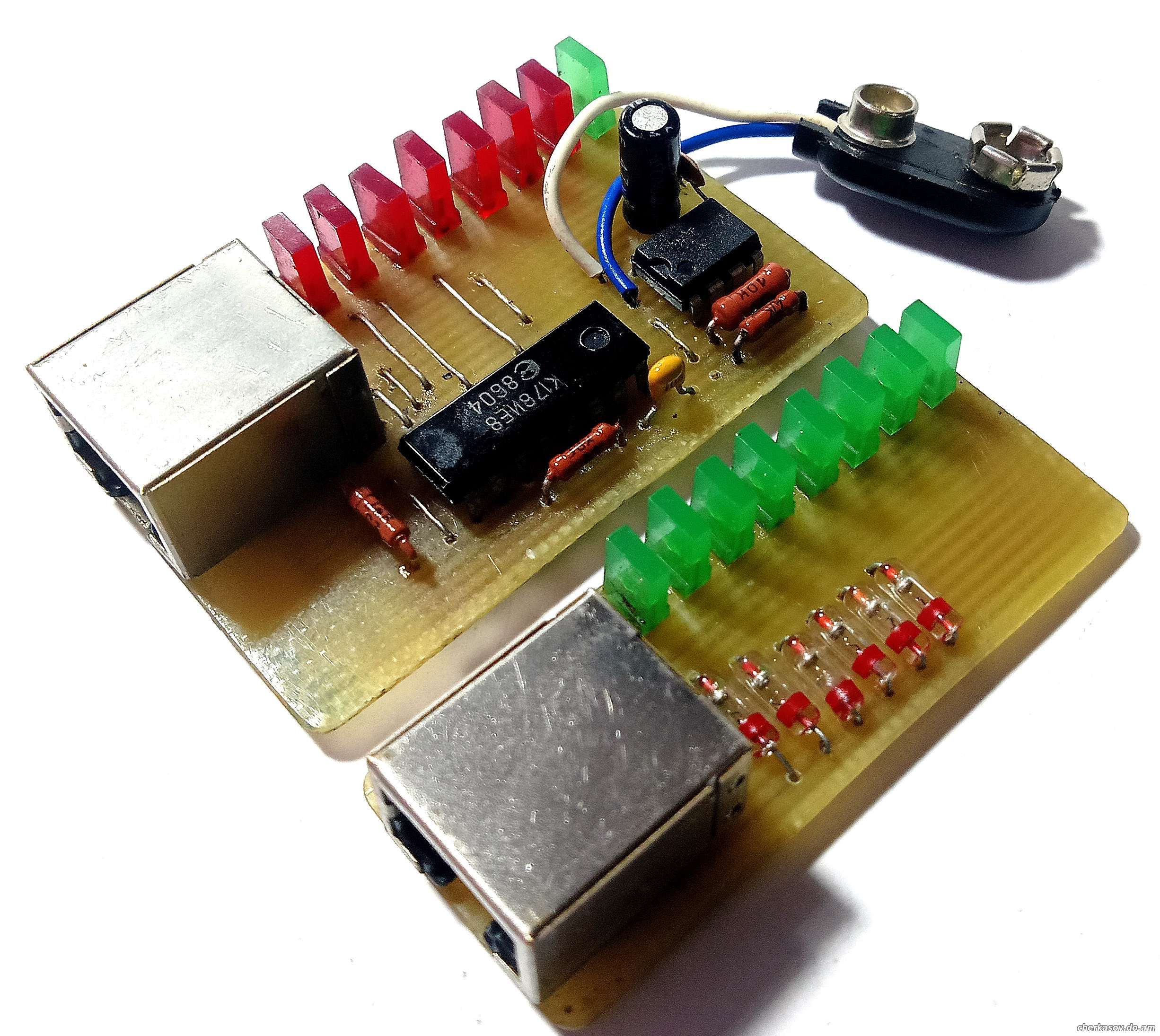

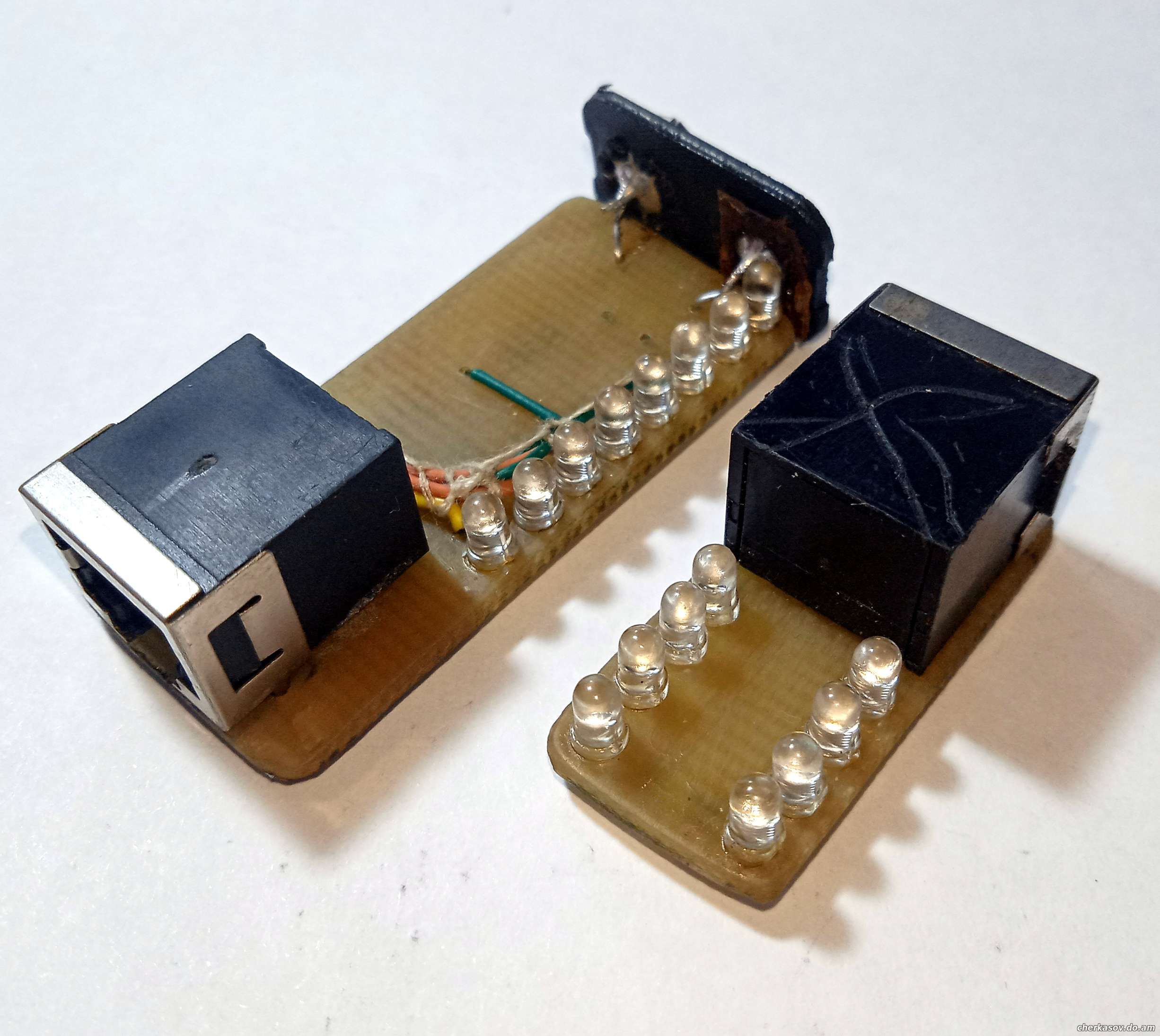

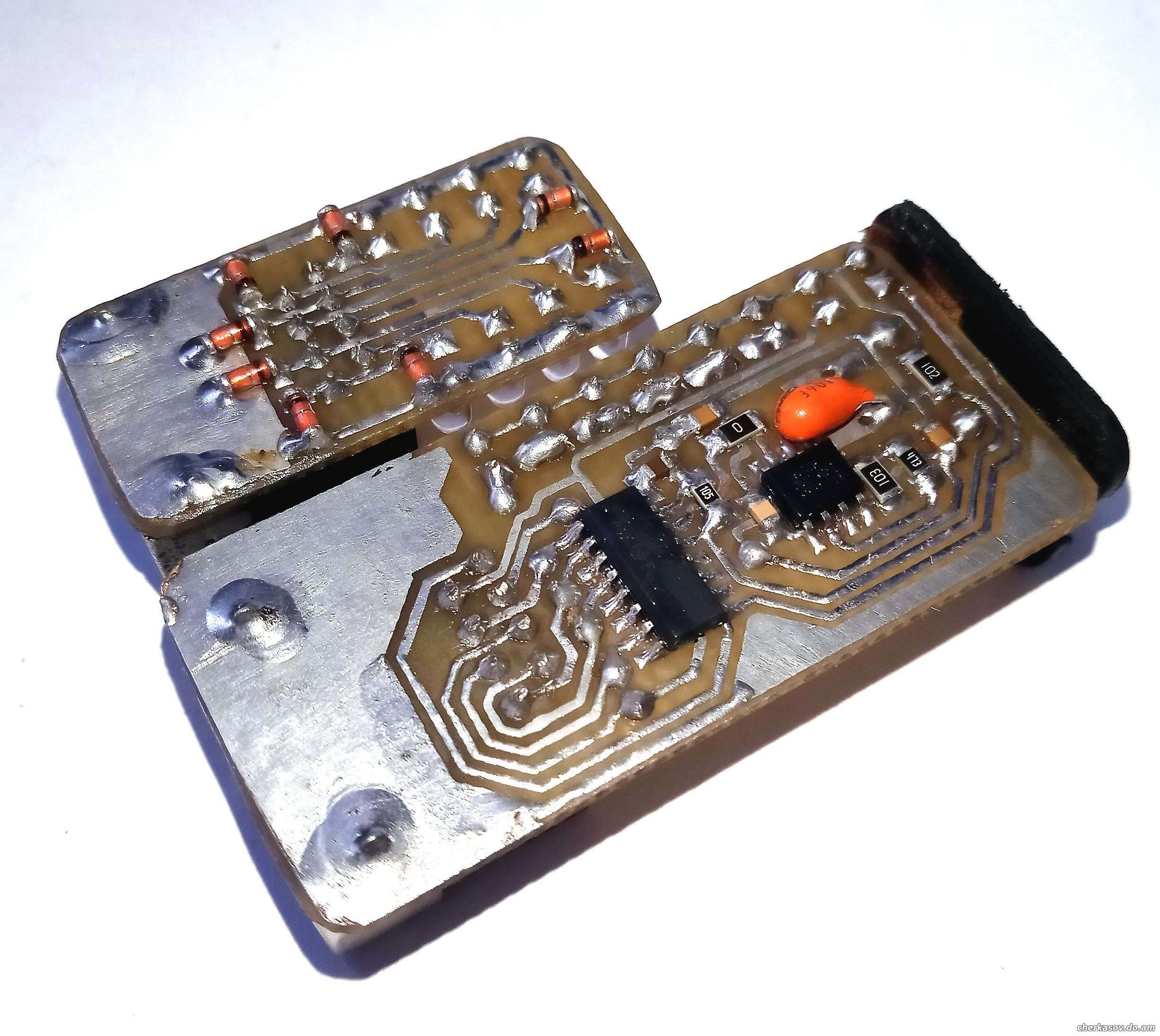

LAN тестер (вторая редакция). И снова тестер витой пары. В моих статьях уже было сказано о нем и приводилась разработка печатных плат и схемы, но время идет элементная база не стоит на месте и пришла необходимость переработать схему и печатную плату. Второй вариант отличается не так схемой, как конструктивными решениями по разработке печатных плат, но обо всем по порядку. В 2019 году одним из интересных проектов для дипломного проектирования стала схема тестера витой пары, при разработке устройства со студентом выпускником мы столкнулись с рядом идей, которые постарались воплотить в жизнь. Проект выполнен в ISIS Proteus и результатом стала рабочая схема с упрощением конструкции и удешевлением стоимости. Так же было принято решение перейти на smd компоненты, как более доступные и современные. В новом варианте мы убираем генератор на логических элементах и собираем по старой, доброй NE555. Импульсы с задающего генератора подаем на двоично-десятичный дешифратор, а далее в линию проверяемого кабеля. Для упрощения схемотехники токоограничивающие резисторы по выходам дешифратора заменяем на один R5. Фильтрующие конденсаторы С4, С5 оставляем, но их можно и упростить. Вместо резисторов R2 и R3 ставим один, подобранный по номиналу для выходной частоты в 1 Гц. Цепь сброса счетчика С6, R4 претерпевает изменение в номиналах. В итоге имеются новая схема с номиналами, два комплекта плат: один в DIP исполнении, а второй в SMD.

Все схемы, спецификация деталей и два комплекта плат вы найдете в архиве статьи. Хочу выразить особую благодарность студентам групп 1КСК-15, 1КСК-16 за вклад в работу сайта, а так же что не даете мне «спокойно спать по ночам» и модернизировать уже имеющиеся схемы. В будущем есть несколько совместных проектов со студентами, которые я так е выложу для повторения будущими поколениями компьютерщиков. | ||||||||

|

| ||||||||

| Всего комментариев: 0 | |